Les processeurs sont devenus de plus en plus rapides au fil des ans grâce à des composants de plus en plus petits. Mais comme nous nous dirigeons vers la limite de la taille des circuits, où allons-nous ? L’une des solutions consiste à fabriquer des puces de la taille d’une plaquette.

Qu’est-ce que la « taille d’une plaquette » ?

Les circuits intégrés tels que les CPU sont créés à partir de cristaux de silicium. Pour créer un dispositif, un énorme cristal de silicium cylindrique est découpé en tranches circulaires. Plusieurs puces sont ensuite gravées sur la surface de la tranche. Une fois que les puces sont terminées, elles sont testées pour trouver les unités défectueuses, et celles-ci sont marquées.

Les puces fonctionnelles sont découpées de la plaquette et emballées en tant que produits finis à vendre. Le » rendement » est le nombre de puces fonctionnelles que vous obtenez à partir d’une plaquette. Toute partie de la tranche qui est gaspillée en raison d’une défaillance des puces ou parce qu’il s’agit d’une chute, doit être récupérée par l’argent gagné grâce aux puces fonctionnelles.

Une puce à l’échelle de la plaquette utilise la totalité de la plaquette pour un seul processeur. L’idée semble géniale, mais quelques problèmes sérieux sont apparus.

ORDINATEURS PORTABLES CHROME AVEC DES PROCESSEURS AMD RYZEN 5000 ULTRA-RAPIDES

Les puces à l’échelle de la plaquette semblaient impossibles à réaliser

Au fil des ans, il y a eu quelques tentatives d' »intégration » d’une tranche de silicium entière. Le problème est que le processus utilisé pour fabriquer les micropuces est imparfait. Sur toute plaquette terminée, il y a forcément des défauts.

Si vous avez imprimé plusieurs copies de la même puce sur une plaquette, quelques exemplaires cassés ne sont pas la fin du monde. Cependant, une seule unité centrale doit être irréprochable pour pouvoir fonctionner. Par conséquent, si vous essayez d’intégrer la totalité de la plaquette, ces défauts inévitables rendront la puce géante inutile.

Pour contourner ce problème, les ingénieurs ont dû repenser la conception d’un processeur massif destiné à fonctionner comme une unité intégrée. Jusqu’à présent, une seule entreprise a réussi à fabriquer un processeur à l’échelle d’une tranche de silicium, et elle a dû résoudre d’importants problèmes techniques pour y parvenir.

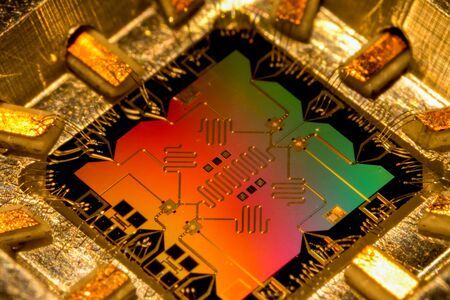

Le Cerebras WSE-2

Le Wafer-Scale Engine 2 de Cerebras Systems est une puce absolument massive. Elle utilise un processus de 7 nm, similaire aux puces de 7 et 5 nanomètres qui équipent divers appareils tels que les smartphones, les ordinateurs portables et les ordinateurs de bureau.

Le WSE-2 est conçu comme un maillage de cœurs qui sont tous reliés les uns aux autres par une grille massive d’interconnexions à haut débit. Ce réseau de modules de cœur de processeur peut tous communiquer, même si certains cœurs sont défectueux. Le WSE est conçu de manière à ce qu’il y ait plus de cœurs que prévu, conformément au rendement attendu de chaque tranche. Cela signifie que, même si chaque puce présente des défauts, ceux-ci n’affectent en rien les performances prévues.

Le WSE-2 est conçu spécifiquement pour accélérer les applications d’IA qui utilisent une technique d’apprentissage automatique appelée « apprentissage profond ». Par rapport aux superordinateurs actuels utilisés pour les tâches d’apprentissage profond, le WSE-2 est plusieurs fois plus rapide, tout en consommant moins d’énergie.

Les avantages des processeurs à l’échelle de la tranche

Les processeurs à l’échelle de la tranche résolvent de nombreux problèmes liés à la conception actuelle des superordinateurs. Les superordinateurs sont construits à partir de nombreux ordinateurs plus petits et plus simples qui sont mis en réseau. En concevant soigneusement les tâches pour ce type de conception, il est possible d’additionner toute cette puissance de calcul.

Cependant, chaque ordinateur de ce réseau de superordinateurs a besoin de ses propres composants de soutien, et l’augmentation de la distance entre les nombreux ensembles de CPU individuels de ce réseau introduit de nombreux problèmes de performance et limite les types de charges de travail qui peuvent être effectuées en temps réel.

Une unité centrale de traitement à l’échelle d’une tranche combine efficacement la puissance de traitement de dizaines ou de centaines d’ordinateurs en un seul circuit intégré, alimenté par une seule alimentation, le tout logé dans un seul châssis. Mieux encore, vous pouvez mettre en réseau plusieurs ordinateurs à l’échelle de la tranche pour créer un superordinateur traditionnel, mais à une vitesse exponentielle.

Des processeurs à l’échelle de la tranche pour le reste d’entre nous ?

Il est peu probable que nous obtenions un produit à l’échelle de la tranche pour les utilisateurs ordinaires qui n’essaient pas de construire un superordinateur, mais certains éléments de la philosophie « plus c’est gros, mieux c’est » sont évidents dans l’électronique grand public également.

Un excellent exemple est le système sur puce (SoC) M1 Ultra d’Apple, qui est constitué de deux SoC M1 Max reliés par une interconnexion à grande vitesse, et qui se présente comme un seul système avec deux fois plus de ressources.

Les conceptions de CPU d’AMD ont également tiré parti des « chiplets », qui sont des unités de cœur de CPU pouvant être fabriquées indépendamment, puis « collées » ensemble à l’aide d’un autre type d’interconnexion à haut débit. Maintenant que les circuits peuvent cesser d’être plus petits sur les CPU, le temps est venu de les construire et peut-être même de les élever, avec des conceptions de circuits complexes en 3D, plutôt que les circuits en 2D plus courants que nous utilisons aujourd’hui.